Sar Adc Logic

Activity Analog To Digital Conversion Analog Devices Wiki

Successive Approximation Adc Explained Youtube

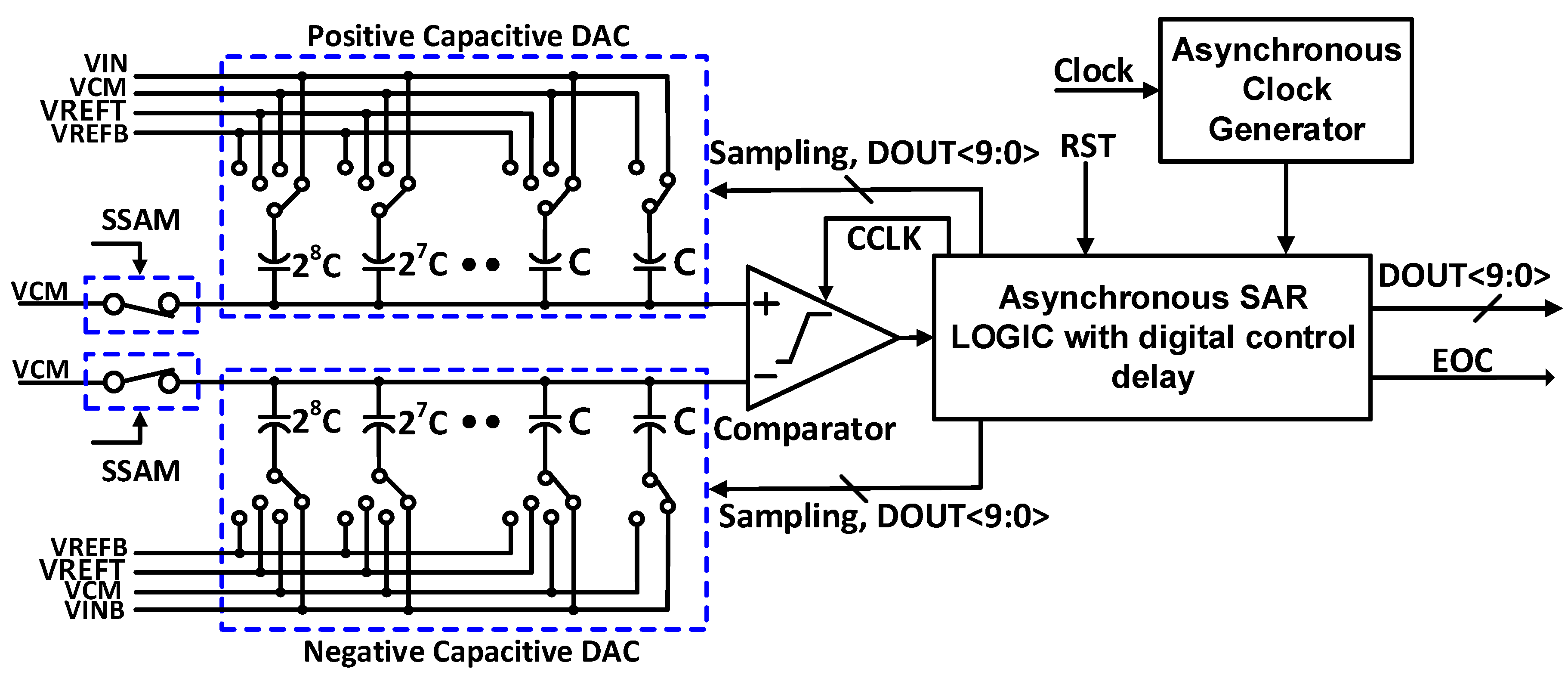

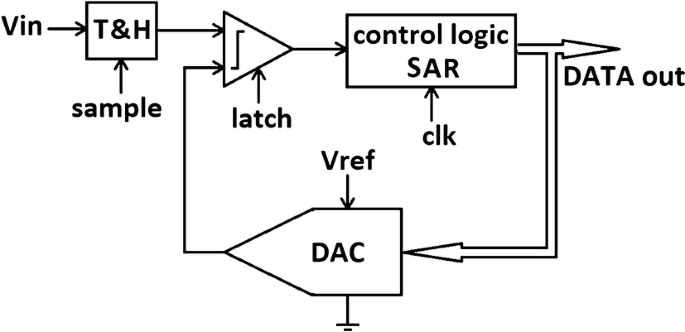

Figure 1 From A 9 Bit 50ms S Asynchronous Sar Adc In 28nm Cmos Semantic Scholar

Sar Adc Logic のギャラリー

Adc Snr Effects Due To Parasitics Mismatch And Noise Edn

Guide To Understanding Successive Approximation Registers Sar And Flash Adcs Maxim Integrated

Q Tbn 3aand9gct2khmcefo5seypm8ou27wavsyu6wtnvmdpztekvct0wbbleu2z Usqp Cau

Time Interleaved Sar Adc Generator Laygo Documentation 1 0 Documentation

Www2 Eecs Berkeley Edu Pubs Techrpts 14 Eecs 14 94 Pdf

Http Nel003 Ee Nthu Edu Tw Nel File 1dd3ade9ab23f32d5dbc9e Pdf

Http Thegrenze Com Pages Servec Php Fn 29 Pdf Name Cadence based imlementation of successiveapproximation adc using 45nm cmos technology Id 1355 Association Mcgraw Hill Conference Mh Icsipca Confyear 17

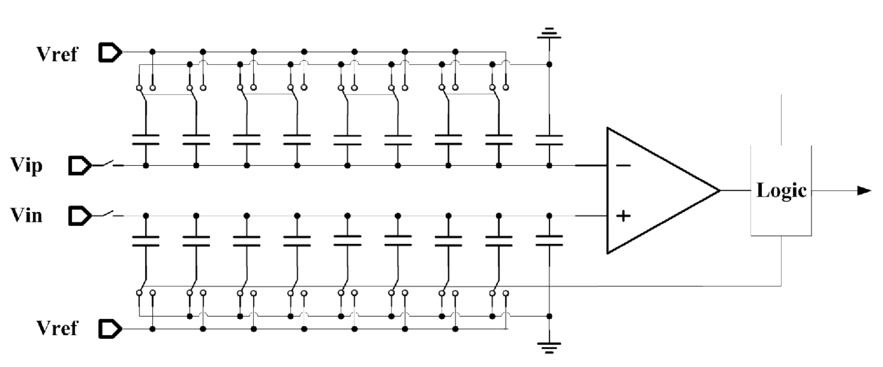

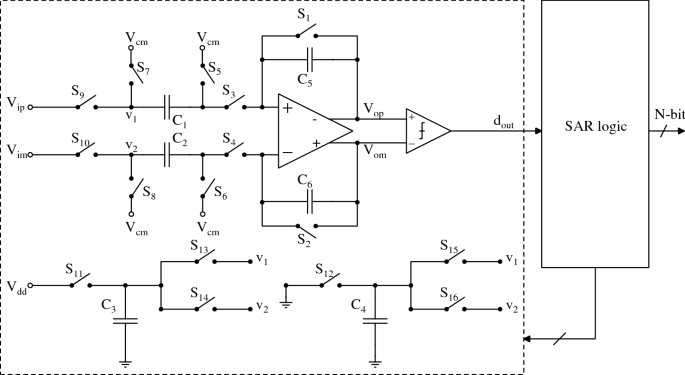

5 4 Bit Fully Differential Switched Capacitor Sar Adc Download Scientific Diagram

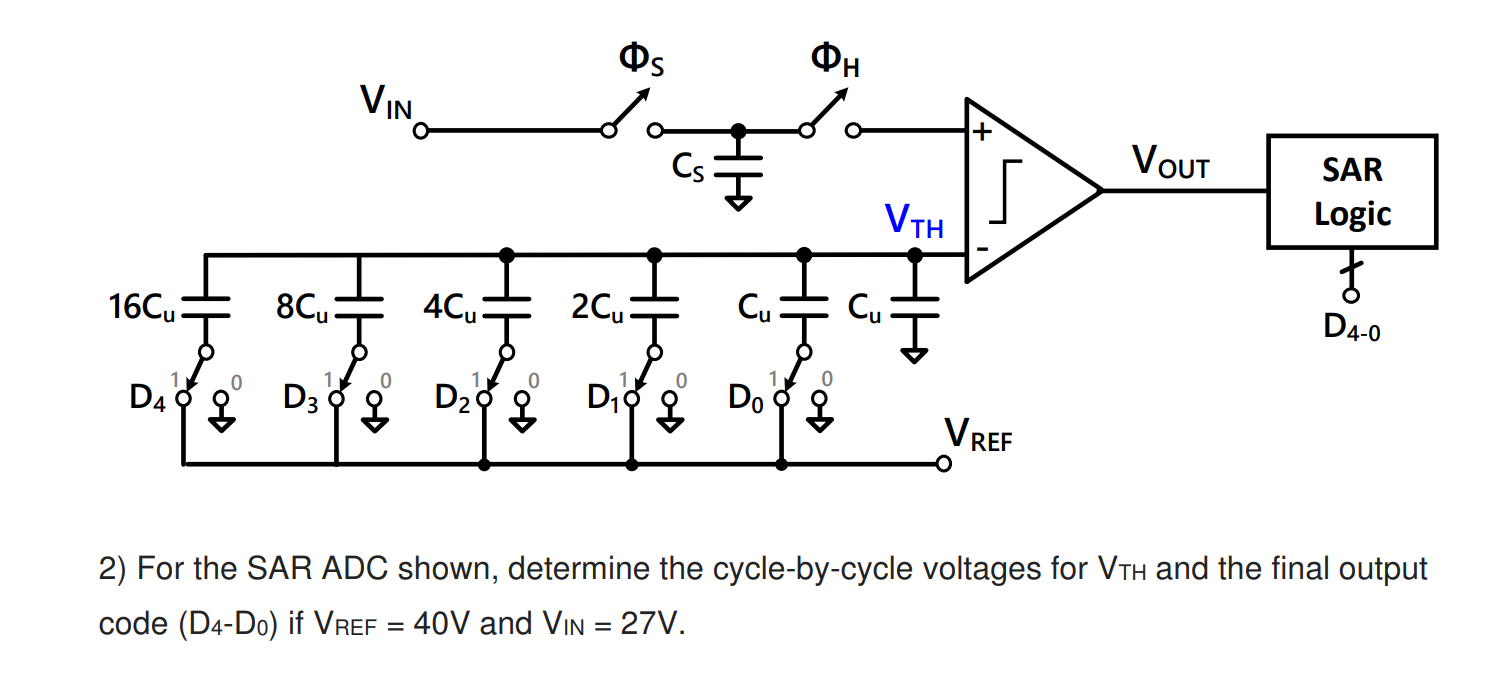

Vino Vout Sar Logic D4 0 160 80 46 24 Cm Dag D Chegg Com

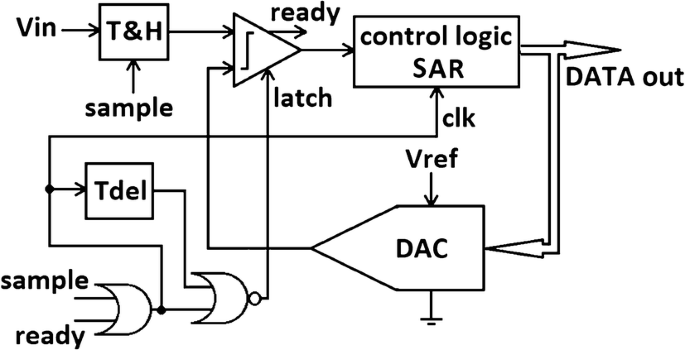

A Semi Synchronous Sar Adc With Variable Dac Settling Time Using A Dll Springerlink

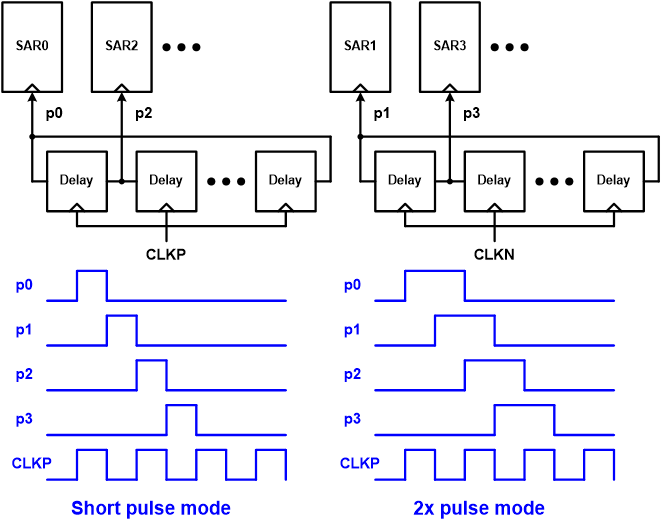

Pulse Generator Of Asynchronous Sar Adc Everynano Counts

Www2 Eecs Berkeley Edu Pubs Techrpts Eecs 109 Pdf

Http Tdata Nongyekx Cn Pdgpath Pdgpath Dll D 2681ee8ade5c0b7d1bc2bd6c3876aaaf7a973a05ba5aa8a1eead7a5c008ca42f29dc9bccec3afb756d65de6dff238f278e2235e3033e6ab0a56b2ccf65c616c5c81bc541b4222d51b N D2 B8 F6 B5 A5 Cd A8 B5 C010 Ce 160 D5 D7 C3 Bf C3 Eb B5 C4 D6 F0 B4 Ce B1 C6 Fc Ca C4 A3 Ca Fd D7 C6 F7

Guide To Understanding Successive Approximation Registers Sar And Flash Adcs Maxim Integrated

Figure 5 From A 7 Bit 26 Ms S Sar Adc In 0 18 Mm Cmos Process For Wsn Application Semantic Scholar

Electronics Free Full Text Design Of A Low Power 10 B 8 Ms S Asynchronous Sar Adc With On Chip Reference Voltage Generator

Pdf Paper Special Section On Analog Circuit Techniques And Related Topics Sar Adc Algorithm With Redundancy And Digital Error Correction Tcg Wu Academia Edu

Http Iopscience Iop Org 1674 4926 34 9 Pdf 1674 4926 34 9 Pdf

Woa1 Sar Adc To Which Secondary Noise Shaping Technique Is Applied Google Patents

A Reconfigurable Dual Mode Tracking Sar Adc Without Analog Subtraction

Adaptive Successive Approximation Adc For Biomedical Acquisition System Sciencedirect

Www Eit Lth Se Sprapport Php Uid 462

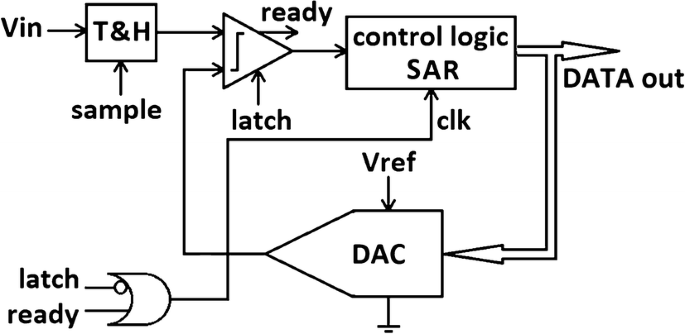

Asynchronous Sar Adc Topology Download Scientific Diagram

Http Www Jsts Org Html Journal Journal Files 17 10 Year17volume17 05 09 Pdf

Ieeexplore Ieee Org Iel7 Pdf

14 Bit Pipeline Sar Adc For Image Sensor Readout Circuits

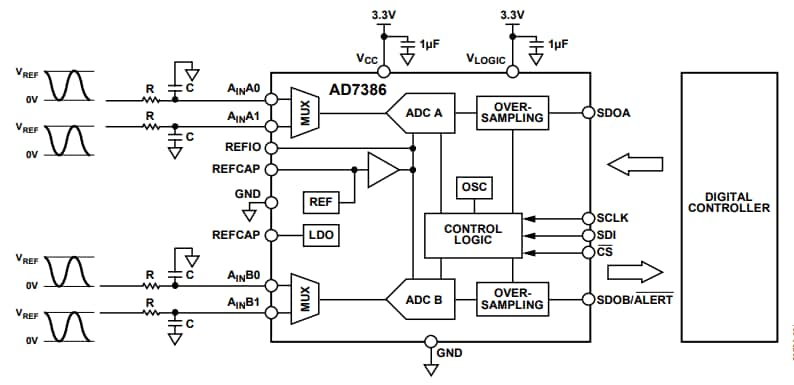

Ad7386 4 Channel 4 Msps 16 Bit Sar Adc Adi Mouser

A 43 6 Db Sndr 1 Gs S 3 2 Mw Sar Adc With Background Calibrated Fine And Coarse Comparators In 28 Nm Cmos

Dual 4 Channel Simultaneous Sampling 12 Bit 3msps Sar Adc

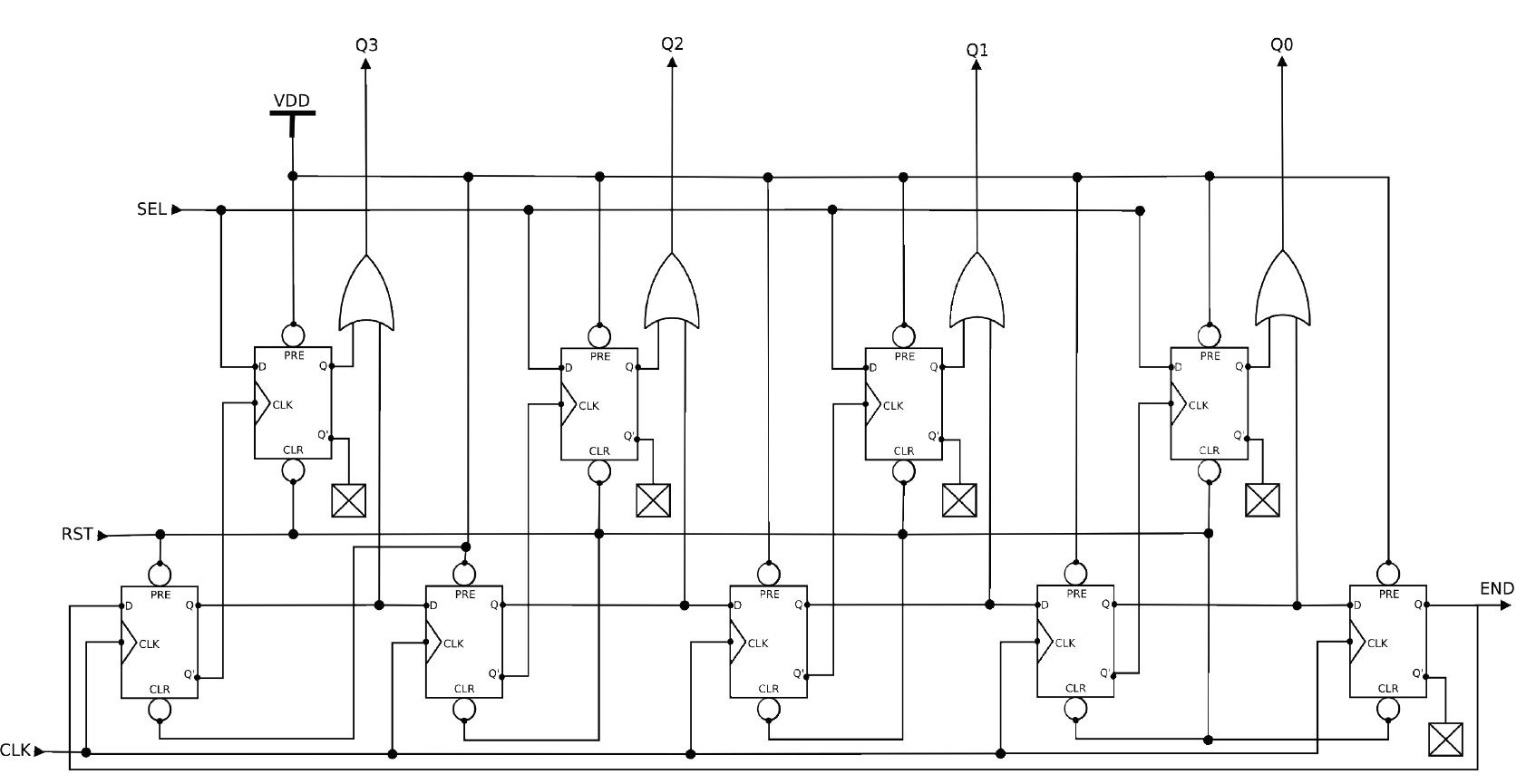

Sar Digital Control Logic Proposed By Anderson 7 Download Scientific Diagram

Http Nel003 Ee Nthu Edu Tw Nel File 1dd3ade9ab23f32d5dbc9e Pdf

Www Ijert Org Research Improved 10 Bit 30 Mss Sar Adc Using Switchback Switching Method Ijertconv3is Pdf

Pulse Generator Of Asynchronous Sar Adc Everynano Counts

N Bit Successive Approximation Register Sar Based Adc Simulink Mathworks Italia

Sar Logic Register Download Scientific Diagram

Sar Logic Register Download Scientific Diagram

Jlpea Free Full Text Review Of Analog To Digital Conversion Characteristics And Design Considerations For The Creation Of Power Efficient Hybrid Data Converters Html

Http Www Jsts Org Html Journal Journal Files 17 10 Year17volume17 05 09 Pdf

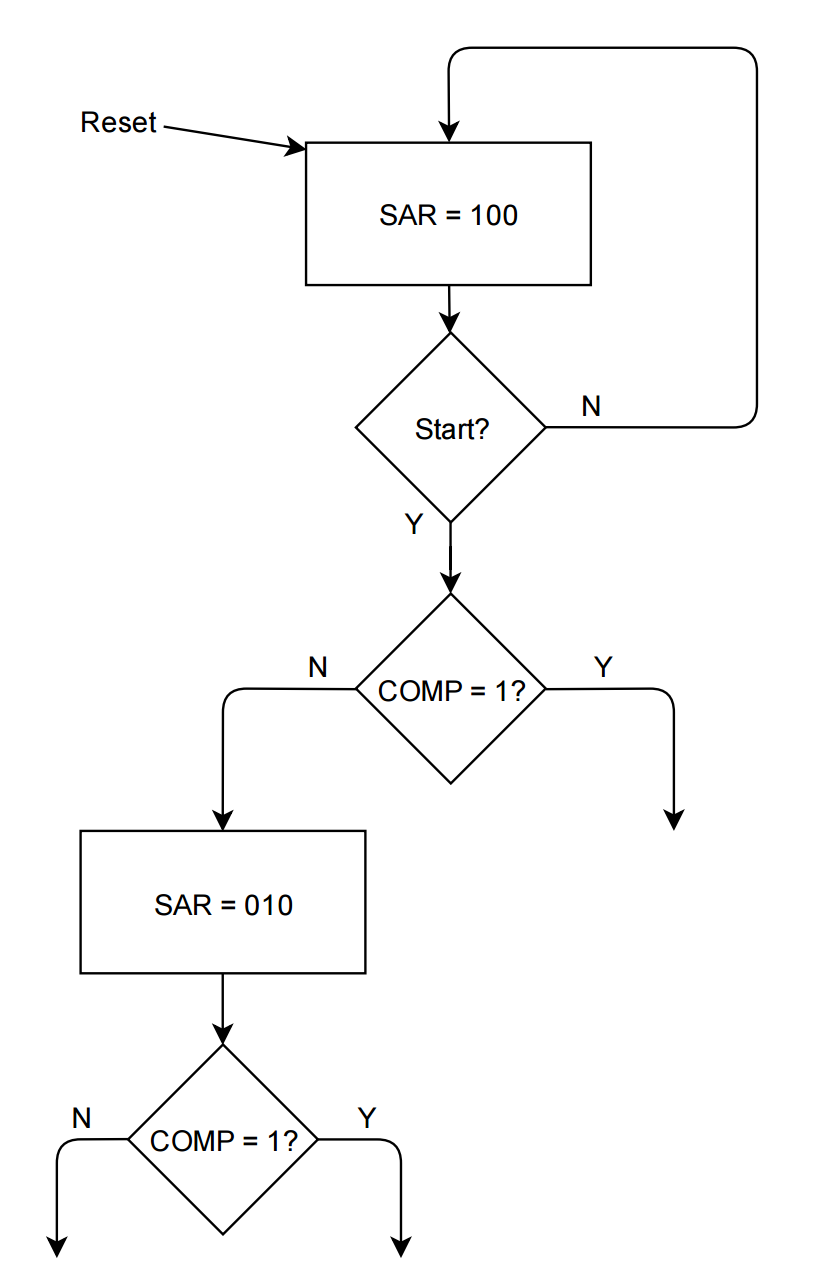

Design And Evaluate Successive Approximation Adc Using Stateflow Matlab Simulink Mathworks America Latina

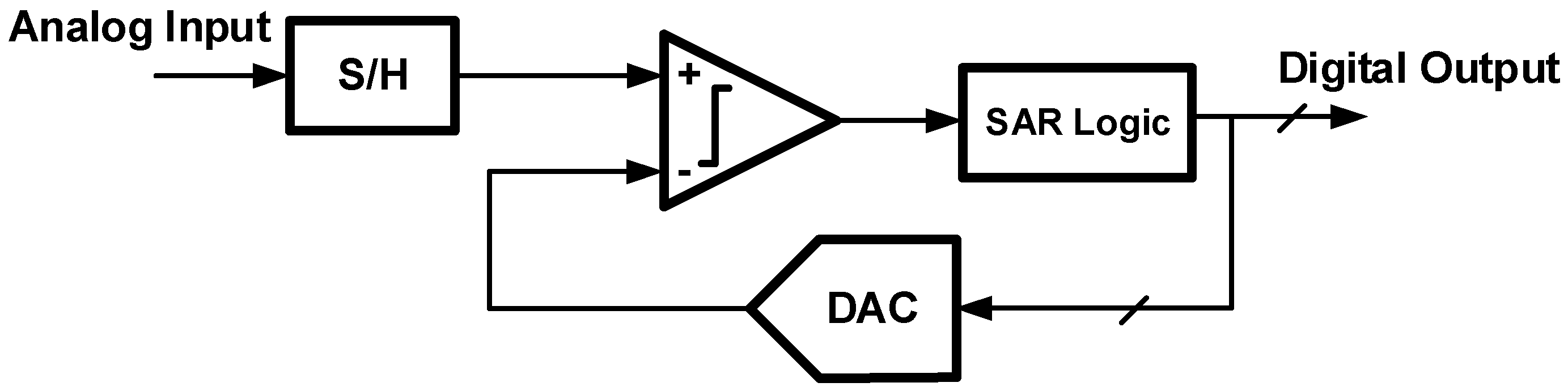

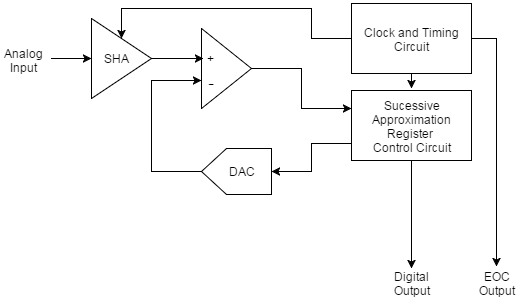

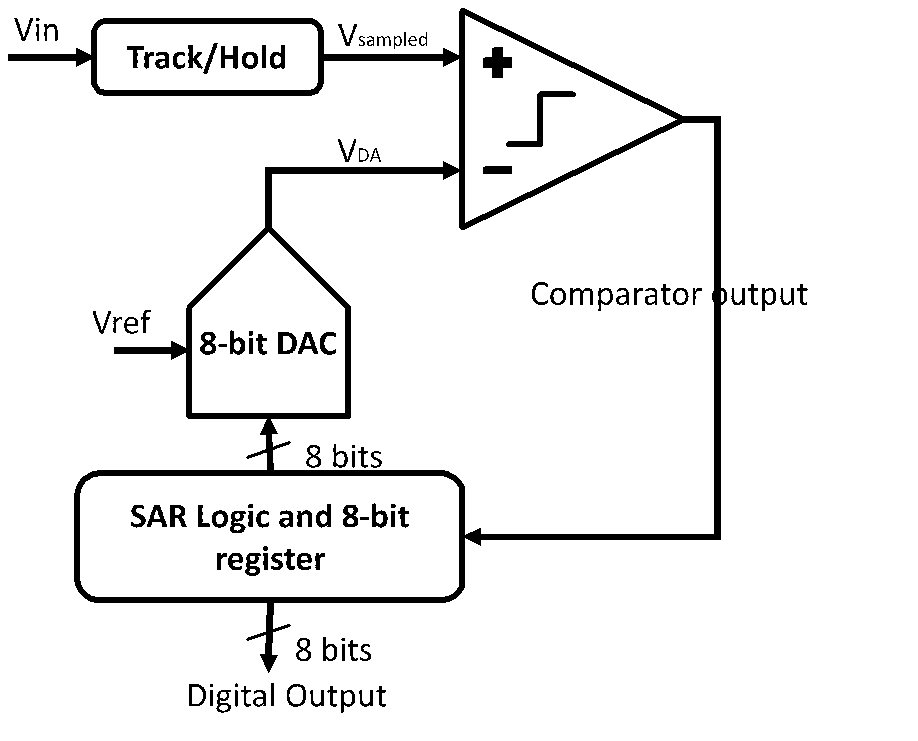

Understanding The Successive Approximation Register Adc Technical Articles

Scholar Smu Edu Cgi Viewcontent Cgi Article 1036 Context Engineering Electrical Etds

Design Of A High Speed 6 Bit Successive Approximate Register Analog To Digital Converter Sar Adc Using 45nm Cmos Technology Analog To Digital Converter Electronic Circuits

Asynchronous Sar Logic Design Using Majority Vote Comparison For Configurable Sar Adcs Semantic Scholar

Uwb Time Interleaved Adc Exploiting Sar

Http Citeseerx Ist Psu Edu Viewdoc Download Doi 10 1 1 303 5776 Rep Rep1 Type Pdf

Implementation Of Integrated Circuit And Design Of Sar Adc For Fully Implantable Hearing Aids Ios Press

Successive Approximation Adc Wikipedia

A Successive Approximation Adc Using Pwm Technique For Bio Medical Applications Intechopen

An Optimized Dac Timing Strategy In Sar Adc With Considering The Overshoot Effect Science Publishing Group

Uwb Time Interleaved Adc Exploiting Sar

Sigma Delta Adc Compared To Sar Adc Developer Help

Guide To Understanding Successive Approximation Registers Sar And Flash Adcs Maxim Integrated

Patent Report Us Pipelined Sar Adc Using Comparator As A Voltage To Time Converter With Multi Bit Second Stage

Eliminate Pipeline Headaches With New 12 Bit 3msps Sar Adc Analog Devices

Fastest 18 Bit Sar Adc Unveiled

Research Tue Nl Files Final Version Pdf

Design Of A New Structure Of Sar Adc Scialert Responsive Version

On The Design Of High Speed Energy Efficient Successive Approximation Logic For Asynchronous Sar Adcs Iopscience

Design And Simulation Of A 6 Bit Successive Approximation Adc Using Modeled Organic Thin Film Transistors

Indico Cern Ch Event 2256 Contributions Attachments Swientek Fcal Krakow Adc Sar 13 04 Pdf

Q Tbn 3aand9gcqopr9kdh Rpyokhk1fw4ubztorbt1x5bzhlkvee4v2nup9cwx4 Usqp Cau

Match The Right Adc To The Application Digikey

Using Sar Adc Tina Models Much Ado About Settling Precision Hub Archives Ti E2e Support Forums

A Compact Power Efficient And Accurate Sar Adc For Ultralow Power Wireless Applications

What Is Adc Converter The Ultimate Guide Dewesoft

Air Supply Lab Analog To Digital Conveter Adc

Learn About Sar Adcs Architecture Applications And Support Circuitry Technical Articles

Successive Approximation Adc Explained Youtube

Research Tue Nl Files Final Version Pdf

Ee6350 Vlsi Design Lab 8 Bit Sar Adc

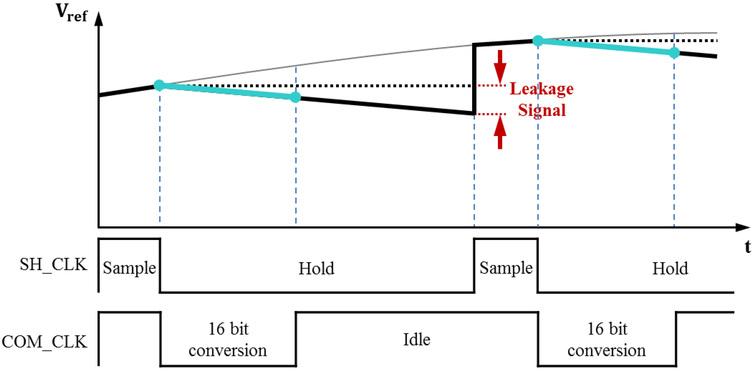

A Semi Synchronous Sar Adc With Variable Dac Settling Time Using A Dll Springerlink

Ee6350 Vlsi Design Lab 8 Bit Sar Adc

Design And Simulation Of A 6 Bit Successive Approximation Adc Using Modeled Organic Thin Film Transistors

Jsts Journal Of Semiconductor Technology And Science

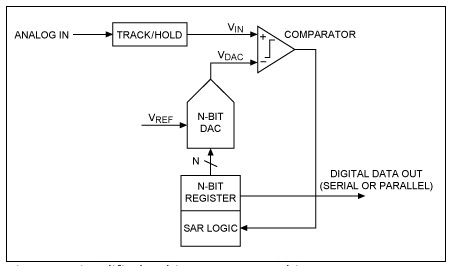

Analog To Digital Conversion

A Semi Synchronous Sar Adc With Variable Dac Settling Time Using A Dll Springerlink

Solved Design A Finite State Machine Which Implements Th Chegg Com

Http Citeseerx Ist Psu Edu Viewdoc Download Doi 10 1 1 300 5603 Rep Rep1 Type Pdf

Ieeexplore Ieee Org Iel7 Pdf

Recent Progress On Cmos Successive Approximation Adcs Matsuura 16 Ieej Transactions On Electrical And Electronic Engineering Wiley Online Library

Sar Adcs Provide Accurate And Reliable Conversion Digikey

Tqm99ar4gsbmpm

Pdf Variation In Power Consumption With Frequency And Voltage Supply For Different Configurations Of Successive Approximation Register Logic Mohamed Aboudina And Karim Abozeid Academia Edu

Q Tbn 3aand9gcrfhbvq4xlosazdm6ppvim5gniow17xsvwfeftubu5hi3xg7csd Usqp Cau

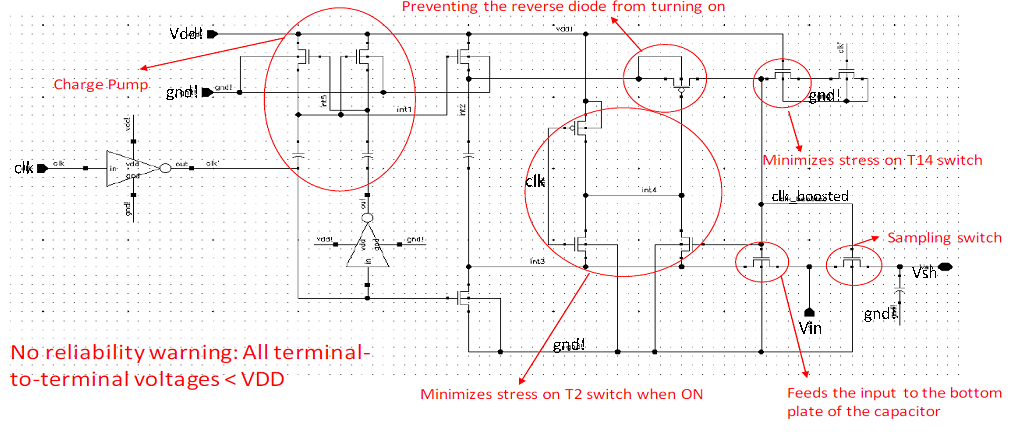

Debugging A 10 Bit Sar Adc Semiwiki

Understanding Sar Adcs

Low Power Sar Adc In 0 18mm Mixed Mode Cmos Process For Biomedical Applications Semantic Scholar

Successive Approximation Register Sar Analog To Digital Converter Adc With Overlapping Reference Voltage Ranges Us 10 432 213 B1 Patentswarm

A 10 Bit 50 Ms S Sar Adc In 65 Nm Cmos With On Chip Reference Voltage Buffer Sciencedirect

A 0 5 V 1 28 Ms S 10 Bit Sar Adc With Switching Detect Logic Semantic Scholar

Schematic Of The Sar Logic Download Scientific Diagram

Modelling And Simulation Of A Sar Adc With Internally Generated Conve

Block Diagram Of The Sar Logic Download Scientific Diagram

A Switched Capacitor Based Sar Adc Employing A Passive Reference Charge Sharing And Charge Accumulation Technique Springerlink

Q Tbn 3aand9gcqzzqixizac3gkadr0zbpahdzyxr3zvn9ilbsuxecsjyvwynwo4 Usqp Cau

Analog To Digital Converters Adc S

Patent Report Us Sar Adc

A Low Cost Digital Domain Foreground Calibration For High Resolution Sar Adcs Sciencedirect

A 0 4 V 10 Bit 10 Ks S Sar Adc In 0 18 Mm Cmos For Low Energy Wireless Senor Network Chip Sciencedirect

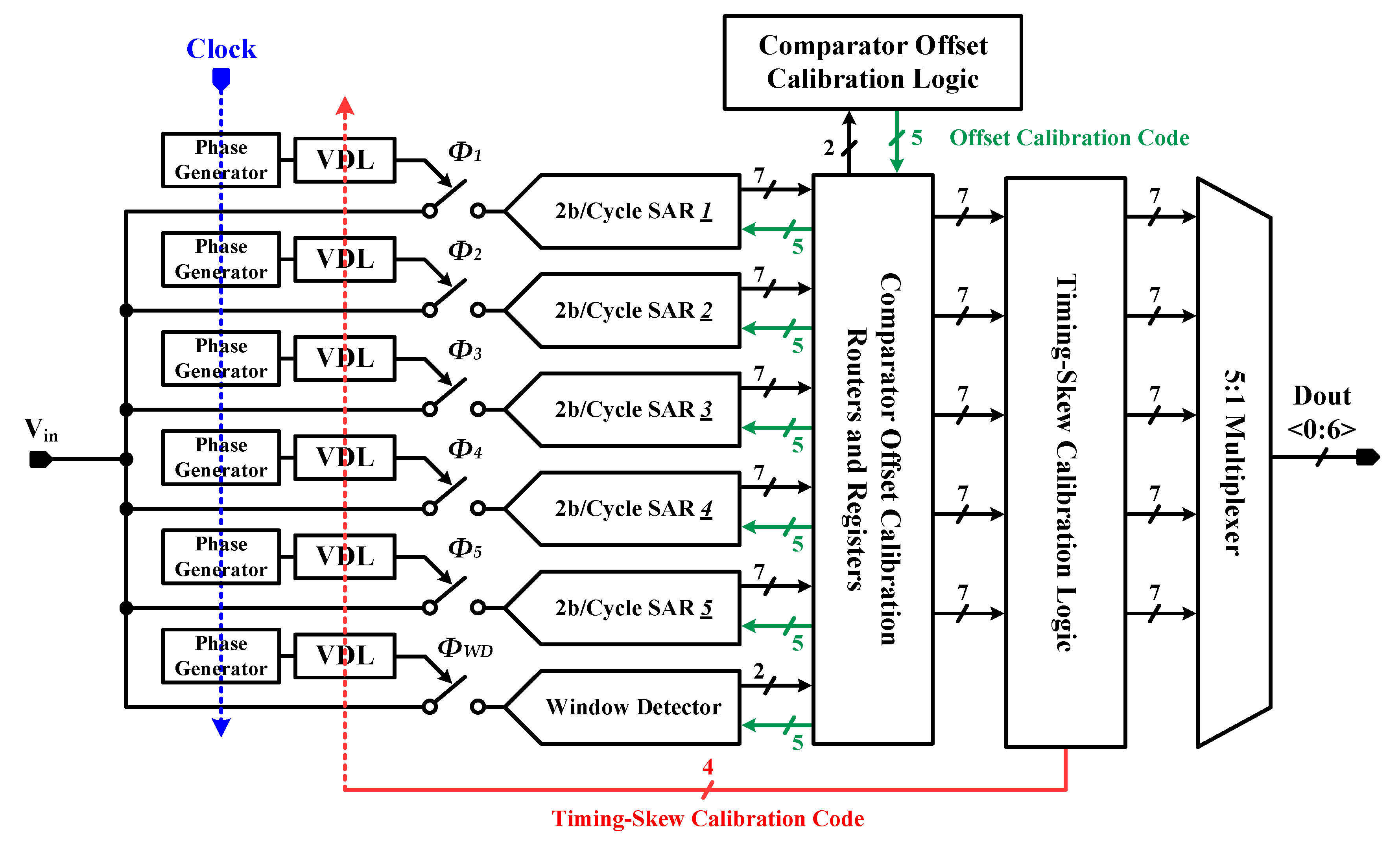

Sensors Free Full Text Time Interleaved Sar Adc With Background Timing Skew Calibration For Uwb Wireless Communication In Iot Systems Html

Block Diagram Of Sar Digital Control Logic Download Scientific Diagram